Intel pitches Clearwater Forest as Xeon consolidation play • The Register

Hot Chips The first datacenter silicon to use Intel’s two-nanometer-class 18A process tech won’t arrive for a while yet, but that’s not stopping the struggling x86 giant from making its sales pitch early.

Speaking at Hot Chips this week, Don Soltis, a Xeon Processor Architect and Intel Fellow, touted a nearly 8:1 consolidation benefit for those upgrading from its six-year-old second-gen Xeon Scalable processors to its next-gen Clearwater Forest systems.

Roughly 1,400 of the aging Xeon systems racks can be compressed into just 180 machines, he said.

Of course, that’s assuming that your workloads don’t require AVX-512 vector acceleration. From what we understand, Clearwater Forest’s 288 slimmed down efficiency cores (e-cores) won’t support the instructions.

As the name suggests, these cores share more in common with the e-cores found in Intel’s consumer CPUs than its mainstream Granite Rapids Xeons.

While it might seem like an odd choice to cram what are essentially a bunch of low-power mobile cores into a server part, for a lot of datacenter workloads, having a ton of good-enough cores beats having a handful of speedy ones, particularly where throughput is key. Webscalers and SaaS vendors take note.

Plus, according to Soltis, the chip’s diet x86 cores will deliver roughly 17 percent more instructions per cycle than its predecessor, thanks in part to significantly wide data paths designed to keep the core utilized.

If Clearwater Forest’s core count sounds familiar, that’s because Clearwater Forest will be Intel’s second chip to offer it, after the 6900E-series Sierra Forest Xeons launched earlier this year.

The way Intel has gone about achieving that core count couldn’t be more different from what it did with Sierra Forest, which had two reticle-sized dies. In the forthcoming Clearwaters, as many as 17 distinct chiplets are stitched together using a combination of Intel’s Foveros 3D and EMIB 2.5D advanced packaging tech.

It’s not all Intel 18A process tech under the hood either. The chipmaker is also using a bunch of Intel 3 and Intel 7 silicon as well.

If you’re getting flashbacks to Intel’s ill-fated Ponte Vecchio GPUs, you’re not alone. But at least this time around it’s an all-Intel affair and a whole lot fewer chiplets.

Working our way down the stack, Clearwater Forest will feature 12 compute dies each with 6 e-core clusters, or slices as Intel prefers to call them. Each of these slices contains four cores along with 4MB of shared L2 cache. In total, each compute die will feature 24 cores.

Moving down a layer, the compute dies are vertically bonded to one of three base dies fabbed on the Intel 3 process node, and are responsible for fabric communications, memory, and apparently some I/O functionality. The chip’s L3 cache is also housed on the base die — 192MB each — which should give you some idea about how confident Intel is about die-to-die latency this time around.

Finally, the base dies are connected to each other along with a pair of I/O dies recycled from Sierra Forest via Intel’s EMIB 2.5D packaging tech. According to Intel, the approach is seamless enough that the chip behaves like a monolithic part, despite having to shuffle bits across 17 different pieces of silicon.

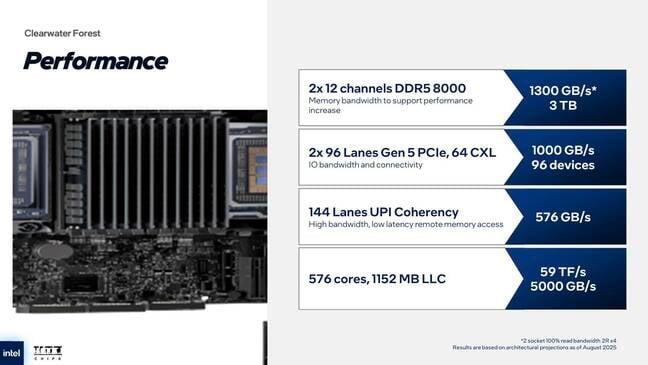

At a platform level, each Clearwater Forest socket will support up to 12 channels of DDR5 8000MT/s memory, and that’s not using the pricy MCRDIMMs touted alongside Intel’s Granite Rapids P-core Xeons either.

For I/O connectivity there aren’t many surprises. Each socket will offer 96 lanes of PCIe 5.0 connectivity with 64 of those lanes offering support for Compute Express Link (CXL) peripherals, which for the moment mostly means cramming DRAM into a PCIe slot.

Like Sierra, Clearwater will be offered in dual socket configurations with up to 576 cores, 3TB of DDR5 and 1.3TB/s of memory bandwidth.

Here’s a quick overview of the speeds and feeds you can expect from Intel’s dual socket Clearwater Forest systems – Click to enlarge

For system integrators, the new chips shouldn’t be too much of a hassle as Intel has elected not to launch them with a new socket — how thoughtful. And while Soltis didn’t divulge specific TDPs for the chip, we already know the 6900-socket can support up to 500 watts.

Winning customers with these core heavy parts won’t be a cakewalk, however, as Intel will need to contend with AMD’s own line of density-optimized Epycs.

You may recall that last fall, AMD unveiled its 192-core Turin-C part. And, despite a lower per-core cache, they’re still a full-fat x86 core with multi-threading and AVX-512 support. While it may be tempting to put Intel’s E-cores and AMD’s Zen 5c cores in the same category, they’re very different approaches in practice.

Clearwater Forest won’t just have to contend with last year’s Epycs either. AMD has already teased its Verano parts, which will offer 256 of what we assume are Zen 6c cores. Both Verano and Clearwater forest are due out sometime next year. ®